System-On-Chip Based on Bare Rocket-chip (RISC-V ISA)

Details

Category: System on Chip

Created: March 04, 2016

Updated: January 27, 2020

Language: VHDL

Other project properties

Development Status: Beta

Additional info: Design done, FPGA proven

WishBone compliant: No

WishBone version: n/a

License: BSD

Description

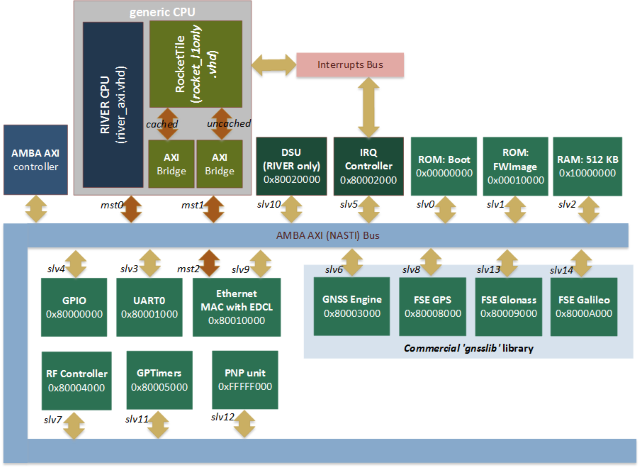

Common top-level structure.

* CPU: Single core "Rocket-chip": 64-bits CPU (RISC-V ISA) with L1/L2 caches, MMU, TLBs, 128-bits data bus and etc.

* General set of peripheries: GPIO, LEDs, UART, IRQ controller etc.

* Portable asynchronous FIFO implementation allowing to connect modules to the System BUS from a separate clock domains (ADC clock domain): Fast Search Engines

* Ethernet MAC 10/100Mb (gigabit MAC by request) with the debug function (EDCL) that allows redirect UDP requests directly on system BUS.

* Debug Support Unit (DSU) provides access to all processors CSRs.

* Satellite navigation modules are distributed as a netlist files (in *.ngc format) or as a stubs.